# **RAM Mapping 32×4 LCD Driver Controller**

# HT1621/1621G

Revision: V3.40 Date: December 13, 2024

www.holtek.com

# **Table of Contents**

| Features                                              | 3  |

|-------------------------------------------------------|----|

| General Description                                   | 3  |

| Selection Table                                       | 3  |

| Block Diagram                                         | 4  |

| Pin Assignment                                        |    |

| Pad Assignment                                        |    |

| Pad Coordinates                                       |    |

| Pad Description                                       | 6  |

| Absolute Maximum Ratings                              |    |

| D.C. Characteristics                                  |    |

| A.C. Characteristics                                  |    |

| Functional Description                                |    |

| Display Memory - RAM                                  |    |

| System Oscillator                                     |    |

| Time Base and Watchdog Timer (WDT)                    |    |

| Tone Output                                           | 11 |

| LCD Driver                                            | 11 |

| Command Format                                        | 12 |

| Interfacing                                           | 12 |

| Crystal Selection                                     | 13 |

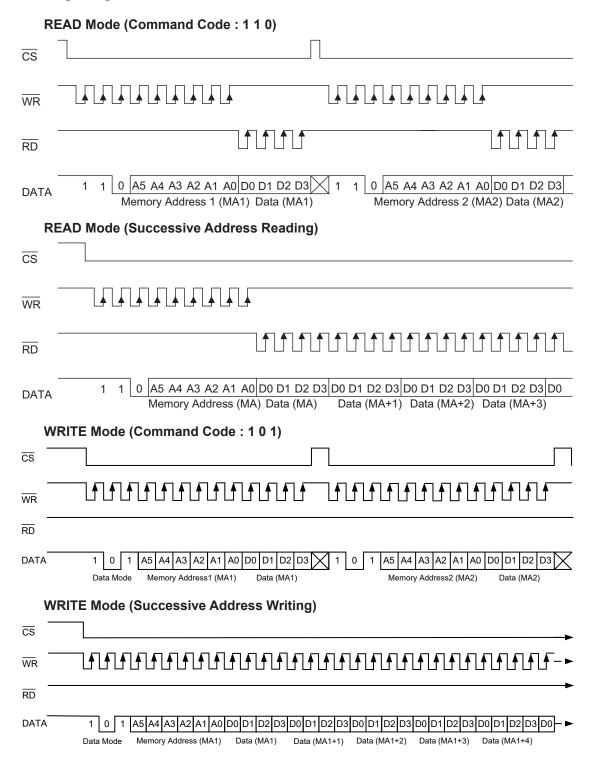

| Timing Diagrams                                       | 14 |

| READ Mode (Command Code : 1 1 0)                      | 14 |

| READ Mode (Successive Address Reading)                | 14 |

| WRITE Mode (Command Code : 1 0 1)                     | 14 |

| WRITE Mode (Successive Address Writing)               |    |

| Read-Modify-Write Mode (Command Code : 1 0 1)         |    |

| Read-Modify-Write Mode (Successive Address Accessing) |    |

| Command Mode (Command Code : 1 0 0)                   |    |

| Mode (Data and Command Mode)                          |    |

| Application Circuits                                  |    |

| Host Controller with an HT1621 Display System         |    |

| Command Summary                                       | 16 |

| Package Information                                   | 18 |

| 44-pin LQFP (10mm×10mm) (FP2.0mm) Outline Dimensions  |    |

| 48-pin SSOP (300mil) Outline Dimensions               |    |

| 48-pin LQFP (7mm×7mm) Outline Dimensions              | 21 |

PATENTED

PAT No. : TW 099352

#### **Features**

• Operating voltage: 2.4V~5.2V

· Built-in 256kHz RC oscillator

- External 32.768kHz crystal or 256kHz frequency source input

- Selection of 1/2 or 1/3 bias, and selection of 1/2 or 1/3 or 1/4 duty LCD applications

- · Internal time base frequency sources

- Two selectable buzzer frequencies (2kHz/4kHz)

- Power down command reduces power consumption

- · Built-in time base generator and WDT

- Time base or WDT overflow output

- 8 kinds of time base/WDT clock sources

- 32×4 LCD driver

- Built-in 32×4 bit display RAM

- 3-wire serial interface

- · Internal LCD driving frequency source

- · Software configuration feature

- Data mode and command mode instructions

- · R/W address auto increment

- Three data accessing modes

- VLCD pin for adjusting LCD operating voltage

- HT1621: 44-pin LQFP package

HT1621B: 48-pin SSOP/LQFP packages

HT1621G: Gold bumped chip

## **General Description**

The HT1621 is a 128 pattern (32×4), memory mapping, and multi-function LCD driver. The S/W configuration feature of the HT1621 makes it suitable for multiple LCD applications including LCD modules and display subsystems. Only three or four lines are required for the interface between the host controller and the HT1621. The HT1621 contains a power down command to reduce power consumption.

#### **Selection Table**

| HT162x        | HT1620   | HT1621    | HT1622 | HT16220 | HT1623    | HT1625    | HT1626   |

|---------------|----------|-----------|--------|---------|-----------|-----------|----------|

| COM           | 4        | 4         | 8      | 8       | 8         | 8         | 16       |

| SEG           | 32       | 32        | 32     | 32      | 48        | 64        | 48       |

| Built-in Osc. | _        | $\sqrt{}$ | √      | _       | $\sqrt{}$ | $\sqrt{}$ | <b>√</b> |

| Crystal Osc.  | <b>V</b> | <b>V</b>  | _      | √       | V         | <b>V</b>  | √        |

Rev. 3.40 3 December 13, 2024

36 SEG12 35 SEG13

34 SEG14

33 SEG15 32 SEG16

31 SEG17

30 SEG18

28 SEG20

27 SEG21 26 SEG22

SGE19

SEG23

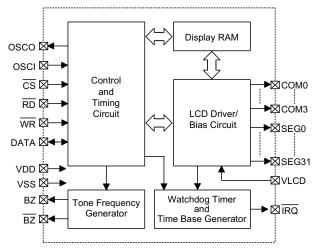

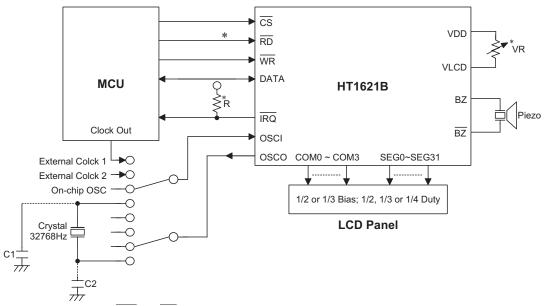

## **Block Diagram**

Note: CS: Chip selection BZ,  $\overline{BZ}$ : Tone outputs

WR, RD, DATA: Serial interface

COM0~COM3, SEG0~SEG31: LCD outputs IRQ: Time base or WDT overflow output

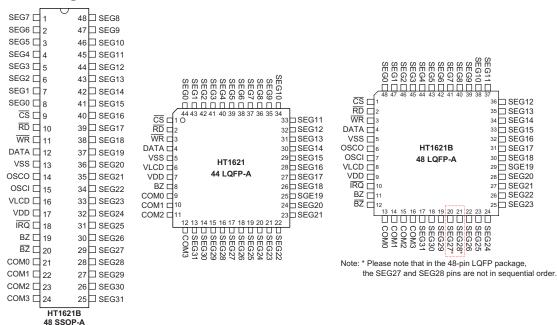

## **Pin Assignment**

Rev. 3.40 4 December 13, 2024

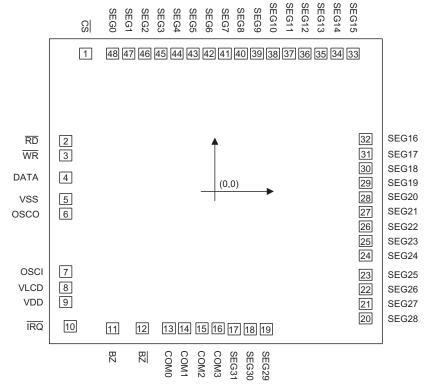

## **Pad Assignment**

Chip size:  $82 \times 83 \text{ (mil)}^2$

Bump height:  $18\mu m \pm 3\mu m$ Min. Bump spacing:  $23.02\mu m$

Bump size:  $76 \times 76 \mu m^2$

Rev. 3.40 5 December 13, 2024

<sup>\*</sup> The IC substrate should be connected to VDD in the PCB layout artwork.

## **Pad Coordinates**

Unit:  $\mu m$

| Pad No. | Х        | Υ        | Pad No. | Х        | Υ        |

|---------|----------|----------|---------|----------|----------|

| 1       | -802.951 | 939.295  | 25      | 925.915  | -338.315 |

| 2       | -927.055 | 343.250  | 26      | 925.915  | -239.255 |

| 3       | -927.055 | 244.230  | 27      | 925.915  | -140.195 |

| 4       | -927.055 | 89.374   | 28      | 925.915  | -41.134  |

| 5       | -925.358 | -52.510  | 29      | 925.915  | 57.925   |

| 6       | -925.358 | -151.360 | 30      | 925.915  | 156.986  |

| 7       | -925.785 | -566.516 | 31      | 925.915  | 256.046  |

| 8       | -925.785 | -675.287 | 32      | 925.915  | 355.106  |

| 9       | -925.699 | -773.697 | 33      | 849.589  | 939.295  |

| 10      | -896.840 | -939-537 | 34      | 750.530  | 939.295  |

| 11      | -637.515 | -935.685 | 35      | 651.469  | 939.295  |

| 12      | -452.726 | -935.685 | 36      | 552.409  | 939.295  |

| 13      | -288.935 | -935.685 | 37      | 453.349  | 939.295  |

| 14      | -189.915 | -935.685 | 38      | 354.289  | 939.295  |

| 15      | -84.350  | -935.685 | 39      | 255.230  | 939.295  |

| 16      | 14.669   | -935.685 | 40      | 156.169  | 939.295  |

| 17      | 114.260  | -940.130 | 41      | 57.109   | 939.295  |

| 18      | 213.320  | -940.130 | 42      | -41.951  | 939.295  |

| 19      | 312.380  | -940.130 | 43      | -141.010 | 939.295  |

| 20      | 925.915  | -867.615 | 44      | -240.070 | 939.295  |

| 21      | 925.915  | -768.555 | 45      | -339.130 | 939.295  |

| 22      | 925.915  | -669.495 | 46      | -438.190 | 939.295  |

| 23      | 925.915  | -570.435 | 47      | -537.250 | 939.295  |

| 24      | 925.915  | -437.375 | 48      | -636.310 | 939.295  |

# **Pad Description**

| Pad No. | Pad Name      | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | <del>CS</del> | I   | Chip selection input with pull-high resistor When the $\overline{CS}$ is logic high, the data and command read from or written to the HT1621 are disabled. The serial interface circuit is also reset. But if $\overline{CS}$ is at logic low level and is input to the $\overline{CS}$ pad, the data and command transmission between the host controller and the HT1621 are all enabled. |  |

| 2       | RD            | I   | READ clock input with pull-high resistor Data in the RAM of the HT1621 are clocked out on the falling edge of the RD signal. The clocked out data will appear on the DATA line. The host controller can use the next rising edge to latch the clocked out data.                                                                                                                            |  |

| 3       | WR            | ı   | WRITE clock input with pull-high resistor Data on the DATA line are latched into the HT1621 on the rising edge of the WR signal.                                                                                                                                                                                                                                                           |  |

| 4       | DATA          | I/O | Serial data input/output with pull-high resistor                                                                                                                                                                                                                                                                                                                                           |  |

| 5       | VSS           | _   | Negative power supply, ground                                                                                                                                                                                                                                                                                                                                                              |  |

| 7       | OSCI          | I   | The OSCI and OSCO pads are connected to a 32.768kHz crystal in order to generate a system clock. If the system clock comes from an external clock source,                                                                                                                                                                                                                                  |  |

| 6       | osco          | 0   | the external clock source should be connected to the OSCI pad. But if an on-chip RC oscillator is selected instead, the OSCI and OSCO pads can be left open.                                                                                                                                                                                                                               |  |

| 8       | VLCD          | ı   | LCD power input                                                                                                                                                                                                                                                                                                                                                                            |  |

| 9       | VDD           | _   | Positive power supply                                                                                                                                                                                                                                                                                                                                                                      |  |

| 10      | ĪRQ           | 0   | Time base or WDT overflow flag, NMOS open drain output                                                                                                                                                                                                                                                                                                                                     |  |

| 11, 12  | BZ, BZ        | 0   | 2kHz or 4kHz tone frequency output pair                                                                                                                                                                                                                                                                                                                                                    |  |

| 13~16   | COM0~COM3     | 0   | LCD common outputs                                                                                                                                                                                                                                                                                                                                                                         |  |

| 48~17   | SEG0~SEG31    | 0   | LCD segment outputs                                                                                                                                                                                                                                                                                                                                                                        |  |

Rev. 3.40 6 December 13, 2024

## **Absolute Maximum Ratings**

| Supply Voltage        | $V_{SS}$ -0.3V to $V_{SS}$ +5.5V |

|-----------------------|----------------------------------|

| Input Voltage         | $V_{SS}$ =0.3V to $V_{DD}$ +0.3V |

| Operating Temperature | -40°C to 85°C                    |

| Storage Temperature   | 60°C to 150°C                    |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **D.C. Characteristics**

Ta=25°C

| Comple at        | Donomoton                  |                 | Test Conditions          | Min  | Тур. | Max. | Unit |

|------------------|----------------------------|-----------------|--------------------------|------|------|------|------|

| Symbol           | Parameter                  | V <sub>DD</sub> | Conditions               | Min. |      |      |      |

| $V_{DD}$         | Operating Voltage          | _               | _                        | 2.4  | _    | 5.2  | V    |

|                  | Operating Current          | 3V              | No load/LCD ON           | _    | 150  | 300  | μA   |

| $I_{DD1}$        | Operating Current          | 5V              | On-chip RC oscillator    | _    | 300  | 600  | μΑ   |

|                  | Operating Current          | 3V              | No load/LCD ON           | _    | 60   | 120  | μΑ   |

| $I_{DD2}$        | Operating Current          | 5V              | Crystal oscillator       | _    | 120  | 240  | μΑ   |

|                  | Operating Current          | 3V              | No load/LCD ON           | _    | 100  | 200  | μΑ   |

| I <sub>DD3</sub> | Operating Current          | 5V              | External clock source    | _    | 200  | 400  | μΑ   |

|                  | Standby Current            | 3V              | No load Dower down made  | _    | 0.1  | 5    | μΑ   |

| I <sub>STB</sub> | Standby Current            | 5V              | No load, Power down mode | _    | 0.3  | 10   | μΑ   |

| VII              | Input Low Voltage          | 3V              | DATA, WR, CS, RD         | 0    | _    | 0.6  | V    |

| VIL              |                            | 5V              | DAIA, WK, CS, KD         | 0    | _    | 1.0  | V    |

| V <sub>IH</sub>  | Innect High Voltage        | 3V              | DATA, WR, CS, RD         | 2.4  | _    | 3.0  | V    |

| VIH              | Input High Voltage         | 5V              | DAIA, WK, CS, KD         | 4.0  | _    | 5.0  | V    |

|                  | DATA, BZ, BZ, IRQ          | 3V              | V <sub>OL</sub> =0.3V    | 0.5  | 1.2  | _    | mA   |

| I <sub>OL1</sub> | DATA, BZ, BZ, IRQ          | 5V              | V <sub>OL</sub> =0.5V    | 1.3  | 2.6  | _    | mA   |

| I <sub>OH1</sub> | DATA, BZ, BZ               | 3V              | V <sub>OH</sub> =2.7V    | -0.4 | -0.8 | _    | mA   |

| IOH1             | DATA, BZ, BZ               | 5V              | V <sub>OH</sub> =4.5V    | -0.9 | -1.8 | _    | mA   |

| I <sub>OL2</sub> | LCD Common Sink Current    | 3V              | V <sub>OL</sub> =0.3V    | 80   | 150  | _    | μΑ   |

| IOL2             | LCD Common Sink Current    | 5V              | V <sub>OL</sub> =0.5V    | 150  | 250  | _    | μΑ   |

| <b>I</b> он2     | LCD Common Source Current  | 3V              | V <sub>OH</sub> =2.7V    | -80  | -120 | _    | μΑ   |

| IOH2             | LCD Common Source Current  | 5V              | V <sub>OH</sub> =4.5V    | -120 | -200 | _    | μΑ   |

|                  | LCD Seament Sink Current   | 3V              | V <sub>OL</sub> =0.3V    | 60   | 120  | _    | μΑ   |

| I <sub>OL3</sub> | LCD Segment Sink Current   | 5V              | V <sub>OL</sub> =0.5V    | 120  | 200  | _    | μΑ   |

| 1                | LCD Cogmont Course Current | 3V              | V <sub>OH</sub> =2.7V    | -40  | -70  | _    | μΑ   |

| I <sub>ОН3</sub> | LCD Segment Source Current | 5V              | V <sub>OH</sub> =4.5V    | -70  | -100 | _    | μΑ   |

| Rph              | Bull high Posistor         | 3V              | DATA, WR. CS. RD         | 60   | 120  | 200  | kΩ   |

| <b>™</b> PH      | Pull-high Resistor         |                 | DAIA, WK, CO, KD         | 30   | 60   | 100  | kΩ   |

## A.C. Characteristics

Ta=25°C

| Cumbal                          | hal Baramatar                                                                                                   |                 | Test Conditions                 |      | T                       | Mary | Unit  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|------|-------------------------|------|-------|

| Symbol                          | Parameter                                                                                                       | V <sub>DD</sub> | Conditions                      | Min. | Тур.                    | Max. | Ullit |

| f <sub>SYS1</sub>               | System Clock                                                                                                    | 3V              | On-chip RC oscillator           | 192  | 256                     | 320  | kHz   |

| f <sub>SYS2</sub>               | System Clock                                                                                                    | _               | Crystal oscillator              | _    | 32768                   | _    | Hz    |

| f <sub>SYS3</sub>               | System Clock                                                                                                    | _               | External clock source           | _    | 256                     | _    | kHz   |

|                                 |                                                                                                                 | _               | On-chip RC oscillator           | _    | f <sub>SYS1</sub> /1024 | _    | Hz    |

| f <sub>LCD</sub>                | LCD Clock                                                                                                       | _               | Crystal oscillator              | _    | f <sub>SYS2</sub> /128  | _    | Hz    |

|                                 |                                                                                                                 | _               | External clock source           | _    | f <sub>SYS3</sub> /1024 | _    | Hz    |

| t <sub>сом</sub>                | LCD Common Period                                                                                               | _               | n: Number of COM                | _    | n/f <sub>LCD</sub>      | _    | s     |

| f                               | Serial Data Clock (WR pin)                                                                                      | 3V              | Duty cycle 50%                  | 4    | _                       | 150  | kHz   |

| f <sub>CLK1</sub>               | Serial Data Clock (WK piri)                                                                                     | 5V              | Duty cycle 50%                  | 4    | _                       | 300  | kHz   |

| £                               | Social Data Clask (DD nin)                                                                                      | 3V              | Duty avala 500/                 | _    | _                       | 75   | kHz   |

| f <sub>CLK2</sub>               | Serial Data Clock (RD pin)                                                                                      | 5V              | Duty cycle 50%                  | _    | _                       | 150  | kHz   |

| £                               | Tone Frequency (2kHz)                                                                                           | 3V              | On-chip RC oscillator           | 1.5  | 2.0                     | 2.5  | kHz   |

| f <sub>TONE</sub>               | Tone Frequency (4kHz)                                                                                           |                 | On-chip No oscillator           | 3.0  | 4.0                     | 5.0  | kHz   |

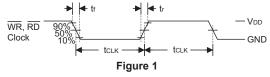

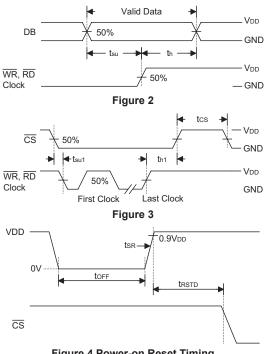

| tcs                             | Serial Interface Reset Pulse<br>Width (Figure 3)                                                                | _               | CS                              | 250  | 300                     | _    | ns    |

|                                 |                                                                                                                 | 2) /            | Write mode                      | 3.34 | _                       | 125  |       |

|                                 | WR, RD Input Pulse Width                                                                                        | 3V              | Read mode                       | 6.67 | _                       | _    | μs    |

| t <sub>CLK</sub>                | (Figure 1)                                                                                                      | 5V              | Write mode                      | 1.67 | _                       | 125  |       |

|                                 |                                                                                                                 |                 | Read mode                       | 3.34 | _                       | _    | μs    |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time Serial Data Clock Width (Figure 1)                                                               | _               | _                               | _    | 120                     | 160  | ns    |

| t <sub>su</sub>                 | Setup Time for DATA to WR, RD Clock Width (Figure 2)                                                            | _               | _                               | 60   | 120                     | _    | ns    |

| t <sub>h</sub>                  | Hold Time for DATA to WR, RD Clock Width (Figure 2)                                                             | _               | _                               | 250  | 300                     | _    | ns    |

| t <sub>su1</sub>                | Setup Time for $\overline{\text{CS}}$ to $\overline{\text{WR}}$ , $\overline{\text{RD}}$ Clock Width (Figure 3) | _               | _                               | 500  | 600                     | _    | ns    |

| t <sub>h1</sub>                 | Hold Time for CS to WR, RD Clock<br>Width (Figure 3)                                                            | _               | _                               | 250  | 300                     | _    | ns    |

| toff                            | V <sub>DD</sub> OFF Time (Figure 4)                                                                             | _               | V <sub>DD</sub> drop down to 0V | 20   | _                       | _    | ms    |

| t <sub>SR</sub>                 | V <sub>DD</sub> Rising Slew Rate (Figure 4)                                                                     | _               | _                               | 0.05 | _                       | _    | V/ms  |

| t <sub>RSTD</sub>               | Delay Time after Reset (Figure 4)                                                                               | _               | _                               | 1    | _                       | _    | ms    |

- Note: 1. If the conditions of Power-on Reset timing are not satisfied in power On/Off sequence, the internal Power-on Reset (POR) circuit will not operate normally.

- 2. If the  $V_{DD}$  drops below the minimum voltage of operating voltage spec. during operating, the conditions of Power-on Reset timing must be satisfied also. That is, the  $V_{DD}$  must drop to 0V and keep at 0V for 20ms (min.) before rising to the normal operating voltage.

Rev. 3.40 8 December 13, 2024

Figure 4 Power-on Reset Timing

## **Functional Description**

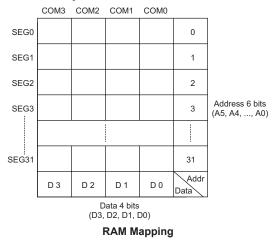

#### **Display Memory - RAM**

The static display memory (RAM) is organized into 32×4 bits and stores the displayed data. The contents of the RAM are directly mapped to the contents of the LCD driver. Data in the RAM can be accessed by the READ, WRITE, and READ-MODIFY-WRITE commands. The following is a mapping from the RAM to the LCD pattern:

Rev. 3.40 9 December 13, 2024

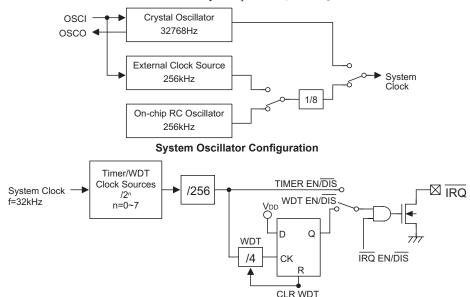

#### **System Oscillator**

The HT1621 system clock is used to generate the time base/Watchdog Timer (WDT) clock frequency, LCD driving clock, and tone frequency. The source of the clock may be from an on-chip RC oscillator (256kHz), a crystal oscillator (32.768kHz), or an external 256kHz clock by the S/W setting. The configuration of the system oscillator is as shown. After the SYS DIS command is executed, the system clock will stop and the LCD bias generator will turn off. That command is, however, available only for the on-chip RC oscillator or for the crystal oscillator. Once the system clock stops, the LCD display will become blank, and the time base/WDT lose its function as well.

The LCD OFF command is used to turn the LCD bias generator off. After the LCD bias generator switches off by issuing the LCD OFF command, using the SYS DIS command reduces power consumption, serving as a system power down command. But if the external clock source is chosen as the system clock, using the SYS DIS command can neither turn the oscillator off nor carry out the power down mode. The crystal oscillator option can be applied to connect an external frequency source of 32kHz to the OSCI pin. In this case, the system fails to enter the power down mode, similar to the case in the external 256kHz clock source operation. At the initial system power on, the HT1621 is at the SYS DIS state.

#### Time Base and Watchdog Timer (WDT)

The time base generator is comprised by an 8-stage count-up ripple counter and is designed to generate an accurate time base. The watch dog timer (WDT), on the other hand, is composed of an 8-stage time base generator along with a 2-stage count-up counter, and is designed to break the host controller or other subsystems from abnormal states such as unknown or unwanted jump, execution errors, etc. The WDT time-out will result in the setting of an internal WDT time-out flag. The outputs of the time base generator and of the WDT time-out flag can be connected to the  $\overline{IRQ}$  output by a command option. There are totally eight frequency sources available for the time base generator and the WDT clock. The frequency is calculated by the following equation.

$$f_{WDT} = \frac{32kHz}{2^n}$$

where the value of n ranges from 0 to 7 by command options. The 32kHz in the above equation indicates that the source of the system frequency is derived from a crystal oscillator of 32.768kHz, an on-chip oscillator (256kHz), or an external frequency of 256kHz.

If an on-chip oscillator (256kHz) or an external 256kHz frequency is chosen as the source of the system frequency, the frequency source is by default prescaled to 32kHz by a 3-stage prescaler. Employing both the time base generator and the WDT related commands, one should be careful since the time base generator and WDT share the same 8-stage counter. For example, invoking the WDT DIS command disables the time base generator whereas executing the WDT EN command not only enables the time base generator but activates the WDT time-out flag output (connect the WDT time-out flag to the IRQ pin). After the TIMER EN command is transferred, the WDT is disconnected from the IRQ pin, and the output of the time base generator is connected to the IRQ pin. The WDT can be cleared by executing the CLR WDT command, and the contents of the time base generator is cleared by executing the CLR WDT or the CLR TIMER command. The CLR WDT or the CLR TIMER command should be executed prior to the WDT EN or the TIMER EN command respectively. Before executing the IRQ EN command the CLR WDT or CLR TIMER command should be executed first. The CLR TIMER command has to be executed before switching from the WDT mode to the time base mode. Once the WDT time-out occurs, the IRQ pin will stay at a logic low level until the CLR WDT or the IRO DIS command is issued. After the IRO output is disabled the IRQ pin will remain at the floating state. The IRQ output can be enabled or disabled by executing the  $\overline{IRQ}$  EN or the  $\overline{IRQ}$  DIS command, respectively. The  $\overline{IRQ}$  EN makes the output

Rev. 3.40 10 December 13, 2024

of the time base generator or of the WDT time-out flag appear on the  $\overline{IRQ}$  pin. The configuration of the time base generator along with the WDT are as shown. In the case of on-chip RC oscillator or crystal oscillator, the power down mode can reduce power consumption since the oscillator can be turned on or off by the corresponding system commands. At the power down mode the time base/WDT loses all its functions.

On the other hand, if an external clock is selected as the source of system frequency the SYS DIS command turns out invalid and the power down mode fails to be carried out. That is, after the external clock source is selected, the HT1621 will continue working until system power fails or the external clock source is removed. After the system power on, the  $\overline{IRQ}$  will be disabled.

**Timer and WDT Configurations**

#### **Tone Output**

A simple tone generator is implemented in the HT1621. The tone generator can output a pair of differential driving signals on the BZ and  $\overline{BZ}$ , which are used to generate a single tone. By executing the TONE 4K and TONE 2K commands there are two tone frequency outputs selectable. The TONE 4K and TONE 2K commands set the tone frequency to 4kHz and 2kHz, respectively. The tone output can be turned on or off by invoking the TONE ON or the TONE OFF command. The tone outputs, namely BZ and  $\overline{BZ}$ , are a pair of differential driving outputs used to drive a piezo buzzer. Once the system is disabled or the tone output is inhibited, the BZ and the  $\overline{BZ}$  outputs will remain at low level.

#### **LCD Driver**

The HT1621 is a 128 (32×4) pattern LCD driver. It can be configured as 1/2 or 1/3 bias and 2 or 3 or 4 commons of LCD driver by the S/W configuration. This feature makes the HT1621 suitable for multiply LCD applications. The LCD driving clock is derived from the system clock. The value of the driving clock is always 256Hz even when it is at a 32.768kHz crystal oscillator frequency, an on-chip RC oscillator frequency, or an external frequency. The LCD corresponding commands are summarized in the table.

The bold form of 1 0 0, namely 1 0 0, indicates the command mode ID. If successive commands have been issued, the command mode ID except for the first command, will be omitted. The LCD OFF command turns the LCD display off by disabling the LCD bias generator. The LCD ON

Rev. 3.40 11 December 13, 2024

## HT1621/1621G RAM Mapping 32×4 LCD Driver Controller

command, on the other hand, turns the LCD display on by enabling the LCD bias generator. The BIAS and COM are the LCD panel related commands. Using the LCD related commands, the HT1621 can be compatible with most types of LCD panels.

| Name       | Command Code         | Function                                                                                                                      |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| LCD OFF    | <b>100</b> 00000010X | Turn off LCD outputs                                                                                                          |

| LCD ON     | <b>100</b> 0000011X  | Turn on LCD outputs                                                                                                           |

| BIAS & COM | <b>100</b> 0010abXcX | c=0: 1/2 bias option<br>c=1: 1/3 bias option<br>ab=00: 2 commons option<br>ab=01: 3 commons option<br>ab=10: 4 commons option |

#### **Command Format**

The HT1621 can be configured by the S/W setting. There are two mode commands to configure the HT1621 resources and to transfer the LCD display data. The configuration mode of the HT1621 is called command mode, and its command mode ID is 1 0 0. The command mode consists of a system configuration command, a system frequency selection command, a LCD configuration command, a tone frequency selection command, a timer/WDT setting command, and an operating command. The data mode, on the other hand, includes READ, WRITE, and READ-MODIFY-WRITE operations. The following are the data mode IDs and the command mode ID:

| Operation         | Mode    | ID    |

|-------------------|---------|-------|

| Read              | Data    | 110   |

| Write             | Data    | 101   |

| Read-Modify-Write | Data    | 1 0 1 |

| Command           | Command | 100   |

The mode command should be issued before the data or command is transferred. If successive commands have been issued, the command mode ID, namely  $1\ 0\ 0$ , can be omitted. While the system is operating in the non-successive command or the non-successive address data mode, the  $\overline{CS}$  pin should be set to "1" and the previous operation mode will be reset also. Once the  $\overline{CS}$  pin returns to "0" a new operation mode ID should be issued first.

#### Interfacing

Only four lines are required to interface with the HT1621. The  $\overline{CS}$  line is used to initialize the serial interface circuit and to terminate the communication between the host controller and the HT1621. If the  $\overline{CS}$  pin is set to 1, the data and command issued between the host controller and the HT1621 are first disabled and then initialized. Before issuing a mode command or mode switching, a high level pulse is required to initialize the serial interface of the HT1621. The DATA line is the serial data input/output line. Data to be read or written or commands to be written have to be passed through the DATA line. The  $\overline{RD}$  line is the READ clock input. Data in the RAM are clocked out on the falling edge of the  $\overline{RD}$  signal, and the clocked out data will then appear on the DATA line. It is recommended that the host controller read in correct data during the interval between the rising edge and the next falling edge of the  $\overline{RD}$  signal. The  $\overline{WR}$  line is the WRITE clock input. The data, address, and command on the DATA line are all clocked into the HT1621 on the rising edge of the  $\overline{WR}$  signal. There is an optional  $\overline{IRQ}$  line to be used as an interface between the host controller and the HT1621. The  $\overline{IRQ}$  pin can be selected as a timer output or a WDT overflow flag output by the S/W setting. The host controller can perform the time base or the WDT function by being connected with the  $\overline{IRQ}$  pin of the HT1621.

Rev. 3.40 12 December 13, 2024

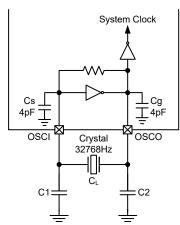

### **Crystal Selection**

A 32768Hz crystal can be directly connected to the HT1621 via OSCI and OSCO. In order to obtain the correct frequency, two additional load capacities (C1, C2) are needed. The value of the capacity depends on how accurate the crystal is. The table illustrates the suggestion value of capacities (C1, C2).

#### Crystal Specifications:

| Symbol   | Parameter         | Min. | Тур.  | Max. | Unit |

|----------|-------------------|------|-------|------|------|

| fo       | Nominal Frequency | _    | 32768 | _    | Hz   |

| Rs (ESR) | Series Resistance | _    | 30    | 50   | kΩ   |

| CL       | Load Capacitance  | _    | 12.5  | _    | pF   |

Note: The oscillator selection can be optimized by using a high quality resonator with a small ESR value.

| Crystal Load Capacitance (C∟)<br>(ESR≤50kΩ) | Load Capacitance of Capacities (C1, C2) (C1=C2) |

|---------------------------------------------|-------------------------------------------------|

| 7pF                                         | 10pF                                            |

| 9pF                                         | 14pf                                            |

| 12.5pF                                      | 21pF                                            |

The C1/C2 capacity value is calculated as follows:

$(C1//C2)=C_L-(Cs//Cg)$ , If C1=C2 and then C1= $(C_L-(Cs//Cg))\times 2$

C<sub>L</sub>: load capacitive for which the crystal

Cs/Cg: integrated load capacitor (Cs=Cg=4pF), (Cs//Cg)=2pF

Rev. 3.40 13 December 13, 2024

## **Timing Diagrams**

Note: It is recommended that the host controller should read in the data from the DATA line between the rising edge of the  $\overline{\text{RD}}$  line and the falling edge of the next  $\overline{\text{RD}}$  line.

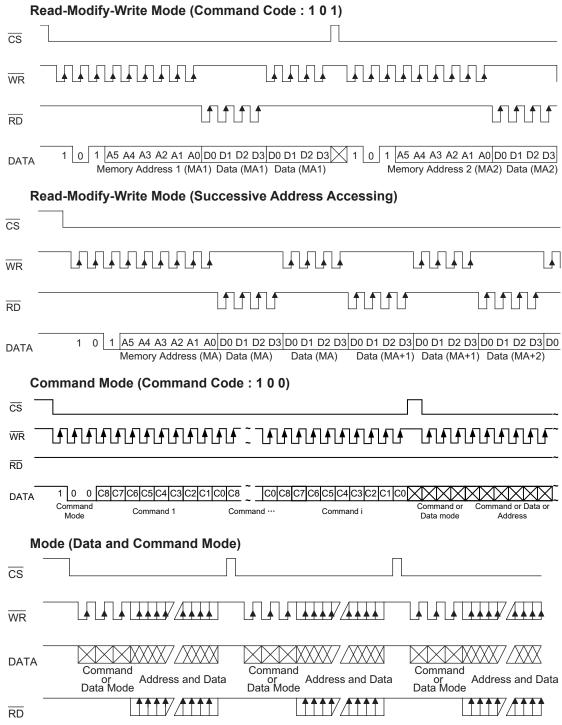

## **Application Circuits**

## Host Controller with an HT1621 Display System

Note: The connection of  $\overline{IRQ}$  and  $\overline{RD}$  pin can be selected depending on the requirement of the MCU.

The voltage applied to  $V_{\text{LCD}}$  pin must be equal to or lower than  $V_{\text{DD}}$ .

Adjust VR to fit user's LCD panel display voltage (V<sub>LCD</sub>).

Adjust R (external pull-high resistance) to fit user's time base clock.

In order to obtain the accuracy of the frequency is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load (C1/C2) for which the crystal was trimmed.

The C1/C2 capacity value is calculated as follows:

$(C1//C2)=C_L-(Cs//Cg)$ , If C1=C2 and then C1= $(C_L-(Cs//Cg))\times 2$

C<sub>L</sub>: load capacitive for which the crystal

Cs/Cg: integrated load capacitor (Cs=Cg=4pf), (Cs//Cg)=2pF

| Crystal Load Capacitance (C∟)<br>(ESR≤50kΩ) | Load Capacitance of Capacities (C1, C2) (C1=C2) |

|---------------------------------------------|-------------------------------------------------|

| 7pF                                         | 10pF                                            |

| 9pF                                         | 14pf                                            |

| 12.5pF                                      | 21pF                                            |

## **Command Summary**

| Name              | ID  | Command Code         | D/C | Function                                                 |     |

|-------------------|-----|----------------------|-----|----------------------------------------------------------|-----|

| READ              | 110 | A5A4A3A2A1A0D0D1D2D3 | D   | Read data from the RAM                                   |     |

| WRITE             | 101 | A5A4A3A2A1A0D0D1D2D3 | D   | Write data to the RAM                                    |     |

| READ-MODIFY-WRITE | 101 | A5A4A3A2A1A0D0D1D2D3 | D   | READ and WRITE to the RAM                                |     |

| SYS DIS           | 100 | 0000-0000-X          | С   | C Turn off both system oscillator and LCD bias generator |     |

| SYS EN            | 100 | 0000-0001-X          | С   | Turn on system oscillator                                |     |

| LCD OFF           | 100 | 0000-0010-X          | С   | Turn off LCD bias generator                              | Yes |

| LCD ON            | 100 | 0000-0011-X          | С   | Turn on LCD bias generator                               |     |

| TIMER DIS         | 100 | 0000-0100-X          | С   | Disable time base output                                 |     |

Rev. 3.40 16 December 13, 2024

| Name      | ID    | Command Code | D/C | Function                                                                                             | Def. |

|-----------|-------|--------------|-----|------------------------------------------------------------------------------------------------------|------|

| WDT DIS   | 100   | 0000-0101-X  | С   | Disable WDT time-out flag output                                                                     |      |

| TIMER EN  | 100   | 0000-0110-X  | С   | Enable time base output                                                                              |      |

| WDT EN    | 100   | 0000-0111-X  | С   | Enable WDT time-out flag output                                                                      |      |

| TONE OFF  | 100   | 0000-1000-X  | С   | Turn off tone outputs                                                                                | Yes  |

| TONE ON   | 100   | 0000-1001-X  | С   | Turn on tone outputs                                                                                 |      |

| CLR TIMER | 100   | 0000-11XX-X  | С   | Clear the contents of time base generator                                                            |      |

| CLR WDT   | 100   | 0000-111X-X  | С   | Clear the contents of WDT stage                                                                      |      |

| XTAL 32K  | 100   | 0001-01XX-X  | С   | System clock source, crystal oscillator                                                              |      |

| RC 256K   | 100   | 0001-10XX-X  | С   | System clock source, on-chip RC oscillator                                                           | Yes  |

| EXT 256K  | 100   | 0001-11XX-X  | С   | System clock source, external clock source                                                           |      |

| BIAS 1/2  | 100   | 0010-abX0-X  | С   | LCD 1/2 bias option<br>ab=00: 2 commons option<br>ab=01: 3 commons option<br>ab=10: 4 commons option |      |

| BIAS 1/3  | 100   | 0010-abX1-X  | С   | LCD 1/3 bias option                                                                                  |      |

| TONE 4K   | 100   | 010X-XXXX-X  | С   | Tone frequency, 4kHz                                                                                 |      |

| TONE 2K   | 100   | 011X-XXXX-X  | С   | Tone frequency, 2kHz                                                                                 |      |

| IRQ DIS   | 100   | 100X-0XXX-X  | С   | Disable IRQ output                                                                                   | Yes  |

| IRQ EN    | 100   | 100X-1XXX-X  | С   | Enable IRQ output                                                                                    |      |

| F1        | 1 0 0 | 101X-X000-X  | С   | Time base/WDT clock output: 1Hz The WDT time-out flag after: 4s                                      |      |

| F2        | 1 0 0 | 101X-X001-X  | С   | Time base/WDT clock output: 2Hz<br>The WDT time-out flag after: 2s                                   |      |

| F4        | 100   | 101X-X010-X  | С   | Time base/WDT clock output: 4Hz The WDT time-out flag after: 1s                                      |      |

| F8        | 100   | 101X-X011-X  | С   | Time base/WDT clock output: 8Hz The WDT time-out flag after: 1/2s                                    |      |

| F16       | 100   | 101X-X100-X  | С   | Time base/WDT clock output: 16Hz The WDT time-out flag after: 1/4s                                   |      |

| F32       | 100   | 101X-X101-X  | С   | Time base/WDT clock output: 32Hz The WDT time-out flag after: 1/8s                                   |      |

| F64       | 100   | 101X-X110-X  | С   | Time base/WDT clock output: 64Hz The WDT time-out flag after: 1/16s                                  |      |

| F128      | 100   | 101X-X111-X  | С   | Time base/WDT clock output: 128Hz The WDT time-out flag after: 1/32s                                 | Yes  |

| TEST      | 100   | 1110-0000-X  | С   | Test mode, user don't use.                                                                           |      |

| NORMAL    | 100   | 1110-0011-X  | С   | Normal mode                                                                                          | Yes  |

Note: X: Don't care

A5~A0: RAM addresses D3~D0: RAM data D/C: Data/command mode

Def.: Power on reset default

All the bold forms, namely 1 1 0, 1 0 1 and 1 0 0, are mode commands. Of these, 1 0 0 indicates the command mode ID. If successive commands have been issued, the command mode ID except for the first command will be omitted. The source of the tone frequency and of the time base/WDT clock frequency can be derived from an on-chip 256kHz RC oscillator, a 32.768kHz crystal oscillator, or an external 256kHz clock. Calculation of the frequency is based on the system frequency sources as stated above. It is recommended that the host controller should initialize the HT1621 after power on reset, for power on reset may fail, which in turn leads to the malfunctioning of the HT1621.

## HT1621/1621G RAM Mapping 32×4 LCD Driver Controller

## **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Further Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- Packing Meterials Information

- Carton information

Rev. 3.40 December 13, 2024

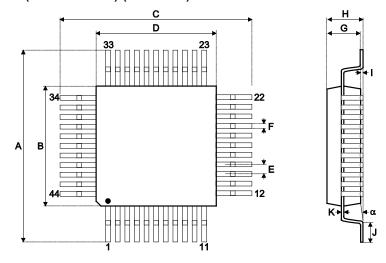

44-pin LQFP (10mm×10mm) (FP2.0mm) Outline Dimensions

| Symbol | Dimensions in inch |       |       |  |

|--------|--------------------|-------|-------|--|

|        | Min.               | Nom.  | Max.  |  |

| A      | 0.472 BSC          |       |       |  |

| В      | 0.394 BSC          |       |       |  |

| С      | 0.472 BSC          |       |       |  |

| D      | 0.394 BSC          |       |       |  |

| E      | 0.032 BSC          |       |       |  |

| F      | 0.012              | 0.015 | 0.018 |  |

| G      | 0.053              | 0.055 | 0.057 |  |

| Н      | _                  | _     | 0.063 |  |

| I      | 0.002              | _     | 0.006 |  |

| J      | 0.018              | 0.024 | 0.030 |  |

| K      | 0.004              | _     | 0.008 |  |

| α      | 0°                 | _     | 7°    |  |

| Symbol | Dimensions in mm |      |      |  |

|--------|------------------|------|------|--|

|        | Min.             | Nom. | Max. |  |

| A      | 12.00 BSC        |      |      |  |

| В      | 10.00 BSC        |      |      |  |

| С      | 12.00 BSC        |      |      |  |

| D      | 10.00 BSC        |      |      |  |

| E      | 0.80 BSC         |      |      |  |

| F      | 0.30             | 0.37 | 0.45 |  |

| G      | 1.35             | 1.40 | 1.45 |  |

| Н      | _                | _    | 1.60 |  |

| I      | 0.05             | _    | 0.15 |  |

| J      | 0.45             | 0.60 | 0.75 |  |

| K      | 0.09             | _    | 0.20 |  |

| α      | 0°               | _    | 7°   |  |

Rev. 3.40 19 December 13, 2024

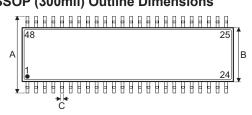

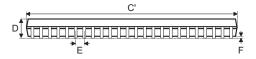

## 48-pin SSOP (300mil) Outline Dimensions

| Symbol | Dimensions in inch |       |       |  |

|--------|--------------------|-------|-------|--|

|        | Min.               | Nom.  | Max.  |  |

| A      | 0.395              | _     | 0.420 |  |

| В      | 0.291              | 0.295 | 0.299 |  |

| С      | 0.008              | _     | 0.014 |  |

| C'     | 0.620              | 0.625 | 0.630 |  |

| D      | 0.095              | 0.102 | 0.110 |  |

| E      | 0.025 BSC          |       |       |  |

| F      | 0.008              | 0.012 | 0.016 |  |

| G      | 0.020              | _     | 0.040 |  |

| Н      | 0.005              | _     | 0.010 |  |

| α      | 0°                 | _     | 8°    |  |

| Symbol | Dimensions in mm |       |       |  |

|--------|------------------|-------|-------|--|

|        | Min.             | Nom.  | Max.  |  |

| Α      | 10.03            | _     | 10.67 |  |

| В      | 7.39             | 7.49  | 7.59  |  |

| С      | 0.20             | _     | 0.34  |  |

| C'     | 15.75            | 15.88 | 16.00 |  |

| D      | 2.41             | 2.59  | 2.79  |  |

| E      | 0.635 BSC        |       |       |  |

| F      | 0.20             | 0.30  | 0.41  |  |

| G      | 0.51             | _     | 1.02  |  |

| Н      | 0.13             | _     | 0.25  |  |

| α      | 0°               | _     | 8°    |  |

Rev. 3.40 20 December 13, 2024

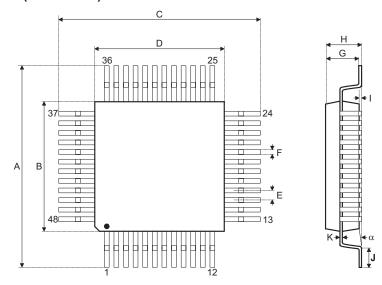

48-pin LQFP (7mm×7mm) Outline Dimensions

| Symbol | Dimensions in inch |           |       |  |  |

|--------|--------------------|-----------|-------|--|--|

|        | Min.               | Nom.      | Max.  |  |  |

| А      | 0.354 BSC          |           |       |  |  |

| В      |                    | 0.276 BSC |       |  |  |

| С      |                    | 0.354 BSC |       |  |  |

| D      | 0.276 BSC          |           |       |  |  |

| Е      | 0.020 BSC          |           |       |  |  |

| F      | 0.007              | 0.009     | 0.011 |  |  |

| G      | 0.053              | 0.055     | 0.057 |  |  |

| Н      | _                  | _         | 0.063 |  |  |

| I      | 0.002              | _         | 0.006 |  |  |

| J      | 0.018              | 0.024     | 0.030 |  |  |

| K      | 0.004              | _         | 0.008 |  |  |

| α      | 0°                 | _         | 7°    |  |  |

| Symbol | Dimensions in mm |      |      |  |

|--------|------------------|------|------|--|

|        | Min.             | Nom. | Max. |  |

| A      | 9.00 BSC         |      |      |  |

| В      | 7.00 BSC         |      |      |  |

| С      | 9.00 BSC         |      |      |  |

| D      | 7.00 BSC         |      |      |  |

| E      | 0.50 BSC         |      |      |  |

| F      | 0.17             | 0.22 | 0.27 |  |

| G      | 1.35             | 1.40 | 1.45 |  |

| Н      | _                | _    | 1.60 |  |

| I      | 0.05             | _    | 0.15 |  |

| J      | 0.45             | 0.60 | 0.75 |  |

| K      | 0.09             | _    | 0.20 |  |

| α      | 0°               | _    | 7°   |  |

Copyright® 2024 by HOLTEK SEMICONDUCTOR INC. All Rights Reserved.

The information provided in this document has been produced with reasonable care and attention before publication, however, HOLTEK does not guarantee that the information is completely accurate. The information contained in this publication is provided for reference only and may be superseded by updates. HOLTEK disclaims any expressed, implied or statutory warranties, including but not limited to suitability for commercialization, satisfactory quality, specifications, characteristics, functions, fitness for a particular purpose, and non-infringement of any thirdparty's rights. HOLTEK disclaims all liability arising from the information and its application. In addition, HOLTEK does not recommend the use of HOLTEK's products where there is a risk of personal hazard due to malfunction or other reasons. HOLTEK hereby declares that it does not authorise the use of these products in life-saving, life-sustaining or safety critical components. Any use of HOLTEK's products in life-saving/sustaining or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold HOLTEK harmless from any damages, claims, suits, or expenses resulting from such use. The information provided in this document, including but not limited to the content, data, examples, materials, graphs, and trademarks, is the intellectual property of HOLTEK (and its licensors, where applicable) and is protected by copyright law and other intellectual property laws. No license, express or implied, to any intellectual property right, is granted by HOLTEK herein. HOLTEK reserves the right to revise the information described in the document at any time without prior notice. For the latest information, please contact us.

Rev. 3.40 22 December 13, 2024